EDSFF (E1.S/E1.L)

E1.S / E1.L Gen 6 Design Challenges

Under the PCIe Gen 6 architecture, EDSFF designs face several critical challenges:

-

PAM4 high-speed signal integrity (SI)

-

Control of insertion loss, return loss, and crosstalk

-

Combined effects of connectors, cables, and PCB stack-up

-

Thermal impact and material stability

-

Correlation between measurement and simulation results

These challenges can no longer be addressed by traditional design experience alone.

They require precise measurement and rigorous engineering validation.

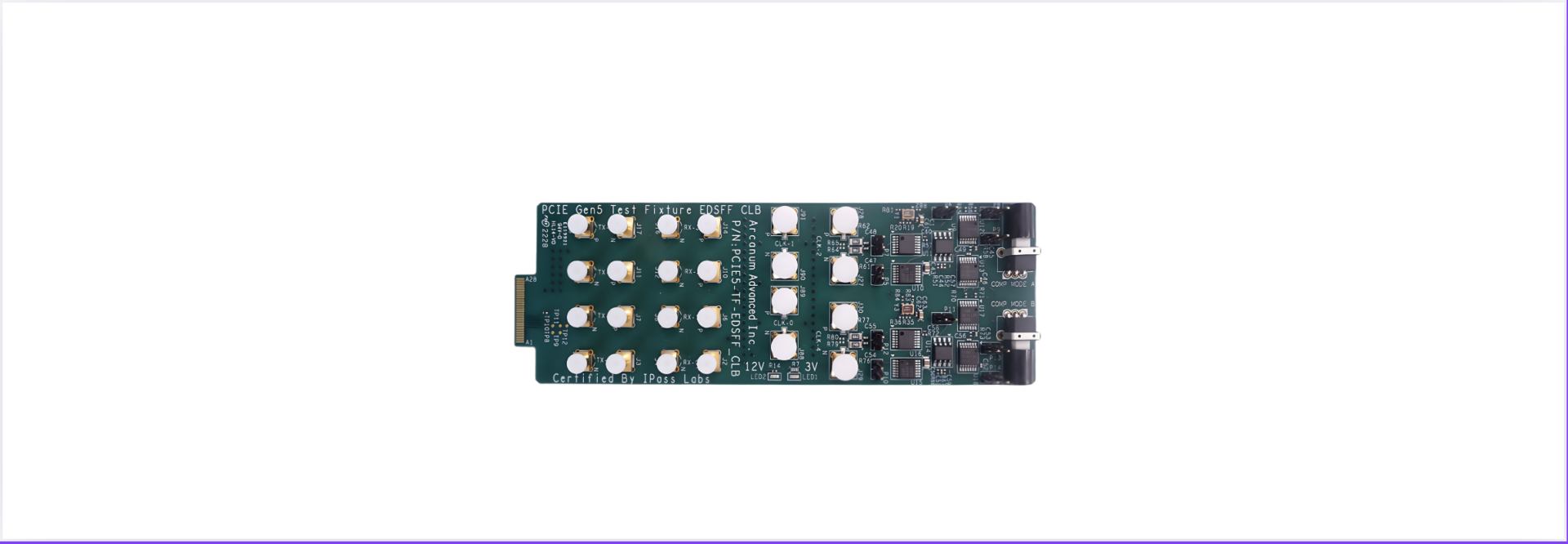

Arcanum Advanced’s Gen 6 Enablement Capabilities

We provide dedicated test and validation solutions tailored for

EDSFF E1.S / E1.L PCIe Gen 6 designs, including:

-

S-parameter, TDR, and eye diagram measurements

-

Delta-L and thermal material stability analysis

-

Connector and fixture de-embedding

-

Channel compliance and correlation validation

-

System-level high-speed channel evaluation

From materials and PCB stack-up to connectors and full channel behavior,

we help customers capture true electrical performance early in the design cycle.